fpga lut是什麼?深入解析FPGA可編程邏輯核心元件 – 查找表(Look-Up Table)的奧秘與應用

Table of Contents

fpga lut是什麼?深入解析FPGA可編程邏輯核心元件 – 查找表(Look-Up Table)的奧秘與應用

當您聽到FPGA(Field-Programmable Gate Array,現場可編程閘陣列)這個詞時,您可能會想到其驚人的彈性與高速運算能力。然而,要理解FPGA為何如此強大,就必須深入探討其最核心、最基礎的邏輯建構單元——查找表(Look-Up Table, LUT)。

本文將帶您一步步揭開FPGA中LUT的神秘面紗,從其基本定義、工作原理、在FPGA中的關鍵作用,到其如何實現各種複雜的數位邏輯功能。透過詳細的解釋與範例,您將對「fpga lut是什麼」有一個全面而深入的理解。

什麼是FPGA?一個快速概覽

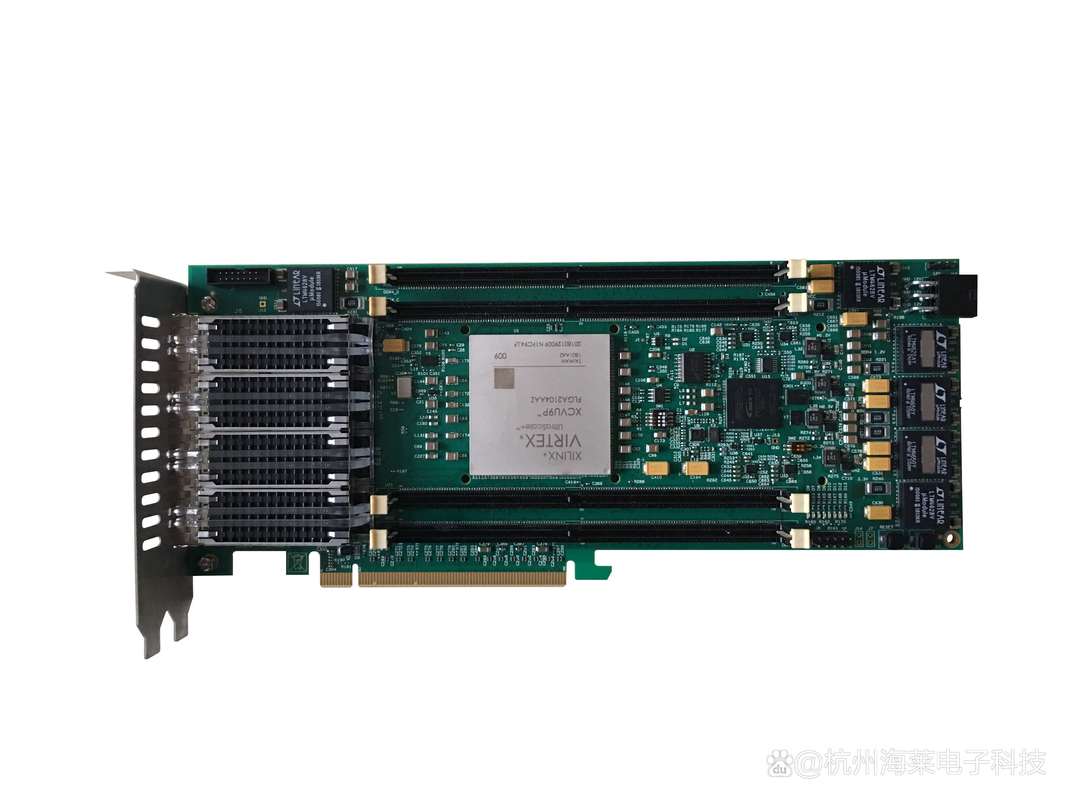

在深入了解LUT之前,讓我們先簡要回顧一下FPGA是什麼。FPGA是一種半客製化積體電路,它不同於傳統的ASIC(特定應用積體電路),後者一旦製造完成,其功能就固定不變。FPGA的獨特之處在於其可編程性,這意味著使用者可以根據自己的需求,對其內部的邏輯電路進行多次配置或重新配置,以實現特定的數位功能。

FPGA的內部結構通常由以下幾大部分組成:

- 可配置邏輯區塊(Configurable Logic Blocks, CLBs)或稱為邏輯單元(Logic Elements, LEs)等:這是實現主要邏輯功能的核心部分,每個CLB內部包含LUT、觸發器(Flip-Flops)及多工器(Multiplexers)等。

- 可編程互連資源(Programmable Interconnects):連接不同邏輯區塊、I/O引腳及其他資源的「電線網」。

- 輸入/輸出區塊(Input/Output Blocks, IOBs):負責FPGA與外部世界的訊號溝通。

- 其他內嵌專用硬體資源:如嵌入式記憶體(Block RAM, BRAM)、數位訊號處理器(DSP Slices)單元、時鐘管理單元(Clock Management Tiles)等。

而我們今天的主角——LUT,正是CLB內部最關鍵的邏輯實現單元。

FPGA LUT是什麼?核心定義與功能

查找表(Look-Up Table, LUT)的基礎概念

查找表(Look-Up Table, LUT)在FPGA中,是一個小型、可編程的記憶體單元,其主要功能是實現任何給定輸入數量的布林邏輯功能。它本質上就像一個預先填寫好的「真值表」,根據輸入訊號的組合,直接「查找」並輸出對應的結果。

換句話說,一個N輸入的LUT可以被配置來實現任何具有N個輸入變數的布林函數。例如,一個4輸入的LUT可以實現任何4個輸入變數的邏輯功能,無論是簡單的AND、OR、XOR閘,還是更複雜的組合邏輯。

LUT如何運作?結構與原理

LUT的工作原理其實相對簡單,但卻極為高效且靈活。其核心結構由以下幾個部分組成:

- SRAM位元(SRAM Cells):這是LUT的「記憶體」部分。對於一個N輸入的LUT,它需要2N個SRAM位元來儲存所有可能的輸入組合所對應的輸出值。這些SRAM位元在FPGA配置時被編程(即寫入0或1),從而定義了LUT所實現的特定邏輯功能。

- 多工器(Multiplexer, MUX):這些輸入訊號直接作為地址線,用於從SRAM記憶體中「查找」對應的輸出值。多工器根據輸入訊號的組合,選擇SRAM中對應地址的數據位元,並將其輸出。

- 輸入訊號(Inputs):這些是邏輯功能的輸入變數,它們同時也是SRAM的地址線。例如,一個4輸入LUT會有4條輸入線。

- 輸出訊號(Output):這是查找表根據輸入訊號組合和其內部SRAM內容所產生的結果。

運作流程簡述:

當輸入訊號的邏輯狀態(高電平或低電平,即1或0)發生變化時,這些輸入訊號會形成一個地址碼,指向LUT內部SRAM記憶體中的某個特定位址。SRAM中這個位址所儲存的數據(0或1)隨即被讀取出來,並作為LUT的輸出。由於SRAM位元的內容可以透過編程來改變,這就使得LUT能夠實現任何使用者定義的邏輯功能。

範例:2-輸入LUT實現AND閘

假設我們有一個2輸入的LUT,我們希望它實現一個AND閘的功能。AND閘的真值表如下:

| 輸入 A | 輸入 B | 輸出 Y (A AND B) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

為了讓這個2輸入LUT實現AND功能,我們需要將其內部的22 = 4個SRAM位元按照AND閘的真值表進行配置:

- 當輸入為(A=0, B=0)時,LUT的SRAM位址00處儲存0。

- 當輸入為(A=0, B=1)時,LUT的SRAM位址01處儲存0。

- 當輸入為(A=1, B=0)時,LUT的SRAM位址10處儲存0。

- 當輸入為(A=1, B=1)時,LUT的SRAM位址11處儲存1。

一旦這樣配置完成,這個LUT就能像一個AND閘一樣工作。當輸入為(1, 1)時,它會查找SRAM位址11,讀出儲存的1,並將其作為輸出。

範例:2-輸入LUT實現XOR閘

同樣是2輸入的LUT,如果我們要實現一個XOR閘(互斥或),其真值表如下:

| 輸入 A | 輸入 B | 輸出 Y (A XOR B) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

這時,2輸入LUT的4個SRAM位元將會被配置為:

- (0,0) -> SRAM位址00處儲存0。

- (0,1) -> SRAM位址01處儲存1。

- (1,0) -> SRAM位址10處儲存1。

- (1,1) -> SRAM位址11處儲存0。

從這兩個範例可以看出,LUT的本質就是一個可配置的真值表。它不依賴於固定的邏輯閘電路結構,而是透過「查找」預存的結果來實現邏輯功能,這賦予了FPGA極高的靈活性。

LUT在FPGA中的重要性與優勢

1. 彈性與可配置性

這是LUT最顯著的優勢。透過簡單地改變SRAM位元中的數據,一個LUT可以實現任何與其輸入數量相符的布林函數,而無需改變FPGA的物理結構。這種高度的彈性是FPGA能夠適應廣泛應用和快速迭代設計的基石。

2. 高度平行處理能力

現代FPGA中包含了數十萬甚至數百萬個LUT。這些LUT可以同時獨立地執行不同的邏輯操作,提供了無與倫比的平行處理能力,這對於資料中心、網路加速、即時影像處理等應用至關重要。

3. 簡化設計與快速原型開發

設計者可以利用硬體描述語言(HDL),如Verilog或VHDL,來描述所需的邏輯功能,然後透過FPGA開發工具鏈(如Xilinx Vivado或Intel Quartus Prime)進行綜合(Synthesis)與佈局(Place & Route)。這些工具會自動將HDL描述的邏輯電路映射到FPGA內部的LUT和其他資源上,大大簡化了複雜數位系統的設計流程,並縮短了產品開發週期。

4. 統一的邏輯實現方式

無論設計者需要實現一個AND閘、一個加法器、一個多工器還是一個複雜的有限狀態機,它們最終都可以被分解並映射到一個或多個LUT上。這種統一的邏輯實現方式簡化了FPGA的內部架構,也方便了製造商的批量生產和設計工具的開發。

5. 易於調試與更新

由於FPGA是可重新編程的,如果在設計中發現錯誤或需要更新功能,只需重新生成配置文件並載入到FPGA中即可,無需重新製造晶片。這使得FPGA成為快速原型開發和產品迭代的理想選擇。

LUT與其他FPGA元件的協同作用

雖然LUT是FPGA的核心,但它並非單獨運作。它與FPGA內的其他元件緊密協作,共同構建出完整的數位系統:

- 觸發器(Flip-Flops, FF):LUT主要用於實現組合邏輯(即輸出僅依賴於當前輸入的邏輯)。而要實現需要記憶狀態的循序邏輯(如計數器、暫存器、有限狀態機),則需要將LUT的輸出與觸發器結合。通常,每個CLB中都會包含幾個LUT和相應的觸發器。

- 佈線資源(Routing Resources):由LUT和觸發器組成的CLB必須透過可編程的互連資源來連接起來,以形成更大型的邏輯電路。這些佈線資源的效率和速度直接影響整個FPGA設計的性能。

- 專用硬體模組:對於某些特定的計算任務,如高速乘法累積運算(MAC operations)和大量的記憶體儲存,FPGA會提供專用的硬體模組(如DSP Slices和Block RAMs)。這些專用模組比用LUT構建相同功能更高效、更快、更省電。LUT則負責連接這些專用模組,並實現它們之間或與外部介面的膠合邏輯。

總結

查找表(Look-Up Table, LUT)是FPGA設計的基石,也是其核心優勢——靈活性和可編程性的關鍵所在。它作為一個小型的可編程記憶體單元,能夠透過簡單地「查找」預存的真值表數據,來高效地實現任何布林邏輯功能。這種設計哲學使得FPGA能夠適應從簡單到複雜的各種數位電路需求,成為數位系統設計中不可或缺的利器。

理解LUT的工作原理,是理解FPGA功能、性能以及如何有效利用其強大能力的關鍵一步。透過LUT與觸發器、佈線資源及其他專用硬體模組的協同作用,FPGA為工程師提供了一個極其強大且靈活的平台,用於快速原型開發、客製化硬體加速以及高效的平行運算。

常見問題 (FAQ)

如何將複雜邏輯電路轉換為LUT的配置?

如何將您用Verilog或VHDL設計的複雜邏輯電路轉換成FPGA中LUT的特定配置呢?這個過程主要是由FPGA設計軟體工具鏈(例如Xilinx Vivado、Intel Quartus Prime)中的「綜合(Synthesis)」階段完成的。綜合工具會將您的高階硬體描述語言代碼翻譯成網表(Netlist),這個網表由基本的邏輯閘(如AND, OR, XOR等)組成。隨後,「映射(Mapping)」階段會將這些基本邏輯閘組合,並高效地映射到FPGA內部的LUT上,決定每個LUT的SRAM位元應該儲存什麼值,從而實現您設計的整體邏輯功能。

為何FPGA製造商要使用LUT,而不是直接使用離散邏輯閘?

為何FPGA製造商選擇使用查找表(LUT)而不是直接構建大量的傳統邏輯閘(如AND、OR閘)來形成FPGA的核心邏輯單元?主要原因是為了達到極致的靈活性和更高的資源利用率。一個N輸入的LUT可以被配置為任何N輸入的布林函數,這比單一功能的離散閘具有更高的通用性。使用LUT可以減少FPGA內部需要佈線的複雜性,並允許更有效率地將邏輯功能打包到有限的硬體資源中。這種設計方式使得FPGA能夠適應多種不同的應用需求,而不必針對每種功能客製化晶片。

如何知道一個FPGA設計使用了多少個LUT?

如何精確地知道您的FPGA設計消耗了多少個LUT資源?在FPGA的設計流程中,當您完成綜合(Synthesis)和佈局佈線(Place & Route)後,FPGA開發工具(如Vivado或Quartus Prime)會生成詳細的資源利用率報告(Resource Utilization Report)。這個報告會清楚地列出您的設計使用了多少個LUT、觸發器、BRAMs、DSPs等各類資源。這對於評估設計是否符合FPGA的容量限制、優化資源使用以及進行功耗估算都非常重要。

為何不同FPGA系列的LUT輸入數量會有所不同(如4-輸入與6-輸入)?

為何在不同的FPGA產品系列中,您會看到LUT的輸入數量有所不同,例如一些是4輸入LUT,另一些是6輸入LUT?這是FPGA製造商在靈活性、性能、晶片面積和功耗之間進行權衡的結果。輸入數量越多的LUT(例如6輸入),其能夠實現的邏輯功能就越複雜,理論上可能需要更少的LUT來實現相同的整體邏輯,從而節省佈線資源並可能提高性能。然而,每個LUT所需的SRAM位元數量是2N(N為輸入數量),所以6輸入LUT(26=64位元)比4輸入LUT(24=16位元)要佔用更多的晶片面積和靜態功耗。製造商會根據目標應用市場(例如高性能運算、低功耗嵌入式系統)來設計不同輸入數量的LUT,以達到最佳的整體平衡。

如何區分LUT與其他記憶體元件(如BRAM)?

如何清楚地區分FPGA中的查找表(LUT)與區塊隨機存取記憶體(Block RAM, BRAM)?儘管兩者都包含SRAM位元,但它們在FPGA中的主要用途和結構特點截然不同。LUT的主要功能是實現布林邏輯功能,它利用少量的SRAM位元作為真值表來查找邏輯結果。它的記憶體是分散且高度並行的,用於小規模的組合邏輯映射。而BRAM則是用於儲存大量數據的專用硬體記憶體塊,其容量通常以KB或MB計,專為高效的讀寫操作設計,例如作為緩衝區、暫存器或資料表。雖然BRAM也可以在某些情況下實現簡單的邏輯查找功能(例如大型真值表),但這不是其主要用途,且效率不如專為邏輯設計的LUT。