FPGA用什麼語言寫?深入解析硬體描述語言與開發流程

「嘿,你 FPGA 的設計進度怎麼樣了?用什麼語言寫的啊?」最近總有朋友在討論 FPGA 設計時,一開口就問到這個問題。這確實是 FPGA 入門者最常遇到的第一個關卡,也是整個 FPGA 開發流程的基石。究竟,FPGA 這個神奇的「可程式化邏輯閘陣列」,我們該用什麼樣的「語言」來跟它溝通,讓它聽懂我們的指令,實現我們想要的數位邏輯功能呢?

別擔心,這篇文章就是要為你解開這個疑惑,並且深入探討 FPGA 設計的語言選擇、開發流程,以及一些你可能沒想到的眉角。作為一個在 FPGA 領域打滾多年的老兵,我深知這個問題的關鍵性,也明白初學者可能面對的迷惘。所以,我會用最平實、最貼近實際操作的方式,一步步帶你了解 FPGA 的「語言世界」。

Table of Contents

FPGA 的「語言」:硬體描述語言 (HDL)

首先,我們要釐清一個觀念:FPGA 並不像我們寫電腦程式那樣,使用 C、Python、Java 這些「軟體」程式語言。FPGA 是一種「硬體」,它的邏輯功能是透過「配置」其內部的邏輯單元和連接線路來實現的。因此,我們用來描述 FPGA 功能的,是所謂的「硬體描述語言」(Hardware Description Language, HDL)。

這就像是我們不是在寫一份文字稿,而是要畫一張詳細的藍圖。HDL 的核心目的,就是用一種結構化、系統化的方式,精確地描述我們希望 FPGA 實現的邏輯功能、電路結構,以及它們之間的工作時序。

目前業界最主流、最被廣泛使用的 HDL 主要有兩種:

- Verilog HDL:源自於 C 語言的語法風格,對於有 C 語言基礎的工程師來說,學習曲線相對平緩。它在語法上比較簡潔,功能強大,被廣泛應用於數位邏輯設計。

- VHDL (VHSIC Hardware Description Language):語法上更接近 Ada 語言,結構嚴謹,具備強大的類型檢查能力,這在大型、複雜的設計中尤其顯著,可以有效減少錯誤。

這兩種語言都可以用來描述 FPGA 的邏輯功能,選擇哪一種,很多時候取決於公司、專案的習慣,或是工程師個人的偏好。不過,如果你的目標是進入業界,了解這兩種語言都是非常有益的。近期也有一些新的 HDL 語言,例如 SystemVerilog,它在 Verilog 的基礎上擴展了許多功能,特別是在驗證 (Verification) 方面,但對於初學者來說,Verilog 和 VHDL 仍是首選。

為什麼選擇 Verilog 或 VHDL?

你可能會問,為什麼我們不能直接用 C 語言來寫 FPGA 呢?這是一個很常見的迷思。原因在於,C 語言是描述「演算法」的,它告訴電腦「如何一步步執行」,而 HDL 則是描述「結構」和「行為」的,它告訴 FPGA「電路長什麼樣子」,以及「電路如何工作」。

你可以想像一下,當你用 C 語言寫一個排序演算法,編譯器會將它轉換成一系列的 CPU 指令。但當你用 Verilog 寫一個加法器,HDL 編譯器 (綜合工具) 會將你的描述轉換成 FPGA 內部邏輯閘的具體連接方式,例如 LUT (Look-Up Table) 的配置、觸發器 (Flip-flop) 的設置等等。這兩種轉換過程是截然不同的。

Verilog 的優勢:

- 語法直觀,類似 C 語言,易於上手。

- 在業界應用非常廣泛,資源和社群支援豐富。

- 靈活性高,可以用於描述從底層的邏輯閘到高層次的模組。

VHDL 的優勢:

- 語法嚴謹,類型檢查嚴格,有助於在設計早期發現錯誤。

- 非常適合大型、複雜的專案,結構清晰,易於維護。

- 標準化程度高,可移植性強。

對我個人來說,剛接觸 FPGA 時,Verilog 的語法讓我感覺更親切,畢竟 C 語言的底子比較厚。但是,隨著專案越來越複雜,VHDL 在大型架構設計中的清晰度和安全性,也讓我刮目相看。現在,許多團隊會混合使用這兩種語言,或者專注於其中一種。重點是,你必須精通其中一種,才能真正駕馭 FPGA。

FPGA 開發的完整流程:從 HDL 到實際晶片

選擇好了語言,下一步就是將我們的設計實現在 FPGA 晶片上。這是一個包含多個嚴謹步驟的流程,每一個環節都至關重要。我可以簡單地將其拆解成以下幾個階段:

1. 設計輸入 (Design Entry)

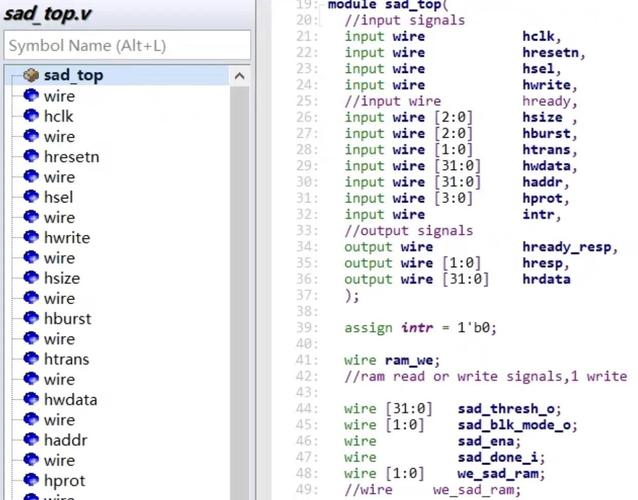

這是我們用 HDL 語言編寫程式碼的階段。就像前面提到的,我們使用 Verilog 或 VHDL 來描述我們想要實現的數位邏輯功能。這可能是一個簡單的計數器、一個通訊協定控制器,甚至是整個嵌入式系統的核心。

範例: 一個簡單的 Verilog 加法器模組,看起來大概是這樣:

module adder (

input [7:0] a,

input [7:0] b,

output [8:0] sum

);

assign sum = a + b;

endmodule

這個範例非常簡單,但它展示了 HDL 的核心:描述輸入、輸出和它們之間的組合邏輯關係。`assign` 語句就是描述一個組合邏輯,直接將 `a` 和 `b` 相加的結果賦予 `sum`。

2. 邏輯綜合 (Logic Synthesis)

這個階段是將我們用 HDL 寫的「抽象」程式碼,轉換成 FPGA 內部可實現的「邏輯閘」和「電路元件」。這個過程是由專業的 EDA (Electronic Design Automation) 工具來完成的,例如 Xilinx 的 Vivado、Intel (Altera) 的 Quartus Prime。綜合工具會讀取我們的 HDL 程式碼,並根據目標 FPGA 的架構,生成一個最佳化的邏輯電路網表 (Netlist)。

重點: 綜合工具會盡量優化電路,使其滿足我們的時序要求,同時縮小面積,降低功耗。但這也意味著,我們寫的 HDL 程式碼,必須是「可綜合 (Synthesizable)」的。也就是說,我們不能隨心所欲地寫,有些 C 語言中的語句(例如,直接存取記憶體位址、迴圈次數不確定的 for 迴圈)在 HDL 中是無法被直接綜合成硬體電路的。

3. 實現 (Implementation)

綜合完成後,我們得到的是一個邏輯電路的網表。接下來的「實現」階段,就是將這個網表「映射」到 FPGA 實際的硬體資源上。這個過程通常包含兩個子步驟:

- 佈局 (Place):決定網表中的每一個邏輯單元 (如 LUT、觸發器) 要放置在 FPGA 晶片上的哪個物理位置。

- 佈線 (Route):將這些放置好的邏輯單元之間的連接線,透過 FPGA 內部的可程式化連接線路實現。

這個階段的目標是找到一個最佳的佈局和佈線方案,以滿足設計的時序要求(最高運行頻率),同時盡量節省 FPGA 的資源。

4. 時序分析 (Timing Analysis)

在 FPGA 設計中,速度(時序)是至關重要的。時序分析工具會根據綜合和實現後的實際佈局佈線結果,精確計算電路中各個路徑的延遲,包括邏輯延遲和線路延遲。最終的目標是確保我們設計的時序約束(例如,最高的時脈頻率)能夠被滿足。如果時序未能滿足,我們就需要回到 HDL 編寫階段,優化我們的設計,或者調整綜合和實現的參數。

5. 生成比特流 (Bitstream Generation)

當所有的設計、綜合、實現和時序檢查都通過後,最後一步就是生成 FPGA 的「比特流」檔案。這個比特流檔案是一個二進制文件,包含了配置 FPGA 內部邏輯單元和連接線路的指令。我們將這個比特流檔案下載到 FPGA 晶片中, FPGA 就能夠按照我們的設計,執行相應的數位邏輯功能了。

6. 硬體驗證 (Hardware Verification)

雖然我們在軟體模擬階段進行了大量的驗證,但最終的驗證還是在實際的 FPGA 硬體上進行。這可以確保我們的設計在真實的硬體環境下能夠正常工作。通常我們會使用邏輯分析儀、示波器等儀器來觀察 FPGA 的輸出信號,或者透過其他介面進行測試。

一些常見的 HDL 陷阱與技巧

在 FPGA 的開發過程中,我遇到過不少新手因為對 HDL 的理解不夠深入而踩過的坑。這裡分享幾個我認為比較重要的:

- 組合邏輯與時序邏輯的混淆:HDL 可以描述組合邏輯(輸出只取決於當前輸入)和時序邏輯(輸出不僅取決於當前輸入,還取決於時脈信號和之前的狀態)。新手常常會混淆兩者的寫法,導致電路行為不符預期。例如,在組合邏輯中不應該使用時脈信號,而在描述時序邏輯時,則必須在 `always @(posedge clk)` 這樣的敏感列表中包含時脈。

- 阻塞性賦值與非阻塞性賦值:在 Verilog 中,`=` 是阻塞性賦值,`<=` 是非阻塞性賦值。這兩者的區別在於,阻塞性賦值會立即更新右側變數的值,影響同一 `always` 塊中後續的語句;而非阻塞性賦值則會在 `always` 塊結束時,一次性更新所有變數的值。這對於描述時序邏輯至關重要。例如,在描述移位暫存器時,必須使用非阻塞性賦值,否則會導致所有位元同時被更新,而無法實現移位效果。

- 過度依賴模擬,忽略綜合限制:模擬 (Simulation) 是驗證 HDL 程式碼邏輯正確性的重要手段,但請務必記住,不是所有在模擬中看起來正確的程式碼,都能被綜合成 FPGA 的硬體。前面提到的「可綜合性」是非常關鍵的。

- 時序約束的重要性:時序約束 (Timing Constraints) 是指導綜合和實現工具優化電路的關鍵。如果你不設定時脈頻率、輸入輸出延遲等約束,工具將無法知道你的設計目標,生成的電路很可能無法達到預期的性能。

FPGA 的「硬體編譯器」:綜合與實現工具

我們在上面提到了 HDL 程式碼的「綜合」和「實現」,這兩個過程離不開專門的 EDA 工具。這些工具可以說是 FPGA 的「硬體編譯器」。

主流的 FPGA 廠商及其開發工具:

- Xilinx (現為 AMD Xilinx):其主要的 FPGA 產品線有 Artix、Kintex、Virtex 等系列。配套的開發工具是 Vivado Design Suite。Vivado 功能強大,涵蓋了從 HDL 編寫、模擬、綜合、實現到配置生成、除錯的全流程。

- Intel (原 Altera):其 FPGA 產品線有 Cyclone、Arria、Stratix 等系列。配套的開發工具是 Quartus Prime。Quartus Prime 也是一個功能全面的開發套件,與 Vivado 類似,提供了一站式的 FPGA 開發解決方案。

這些工具本身就非常複雜,有著龐大的功能和設定選項。初學者往往需要花費不少時間去熟悉它們的操作界面和基本設定。理解這些工具如何將 HDL 程式碼轉換成 FPGA 的配置,對於設計除錯和性能優化至關重要。

除錯的藝術:軟體模擬與硬體除錯

在 FPGA 開發中,除錯 (Debugging) 是一個貫穿始終的環節。當設計不工作時,我們需要找到問題所在,並加以修正。除錯主要有兩種方式:

- 軟體模擬 (Software Simulation):我們可以使用 HDL 模擬器(如 Modelsim、Questa、Xcelium,或 Vivado、Quartus 自帶的模擬器)來執行我們的 HDL 程式碼。模擬器會根據我們提供的測試平台 (Testbench),模擬設計在不同輸入下的輸出行為,並產生波形圖 (Waveform)。我們可以透過觀察波形圖,來判斷設計的邏輯是否正確。

- 硬體除錯 (Hardware Debugging):當設計在 FPGA 實際運行時出現問題,軟體模擬無法完全覆現時,我們就需要藉助硬體除錯工具。例如,Xilinx 的 Vivado 提供了 ILA (Integrated Logic Analyzer),Intel 的 Quartus Prime 提供了 SignalTap。這些工具允許我們在 FPGA 內部嵌入一個邏輯分析儀,讓我們能夠即時捕捉 FPGA 內部關鍵信號的波形,就像在硬體上接了一個示波器一樣。

對我來說,軟體模擬是驗證基本邏輯的第一道防線,它能幫我們快速排除大部分的邏輯錯誤。而硬體除錯則是在最終驗證和解決那些「看似正確,卻在硬體上掛掉」的問題時,不可或缺的利器。能夠熟練運用這些除錯工具,是 FPGA 工程師必備的技能。

FPGA 用什麼語言寫?總結與您的下一步

回到最初的問題:「FPGA 用什麼語言寫?」答案是:主要使用硬體描述語言 (HDL),其中最常見的是 Verilog HDL 和 VHDL。

這些語言讓我們能夠精確地描述 FPGA 的硬體結構和工作行為,然後透過專業的 EDA 工具,將這些描述轉換成 FPGA 晶片上實際的配置。這是一個從抽象到具體的過程,也是一個將軟體思維轉化為硬體實現的過程。

如果您剛開始接觸 FPGA,我會建議您:

- 選擇一種 HDL 語言入門:可以先從 Verilog 入手,因為它相對容易上手。

- 掌握基本的 HDL 語法和特性:理解組合邏輯、時序邏輯、可綜合性等概念。

- 熟悉主流的 FPGA 開發工具:例如 Xilinx Vivado 或 Intel Quartus Prime,至少要學會如何建立專案、編寫程式碼、執行綜合、實現和下載。

- 動手實踐:從簡單的邏輯電路(如 LED 閃爍、按鈕控制)開始,逐步挑戰更複雜的設計。

- 學習除錯技巧:學會使用軟體模擬器和硬體除錯工具。

FPGA 設計是一個充滿挑戰但也極具回報的領域。它結合了軟體編程的抽象思維和硬體電路的精確控制。希望這篇文章能為你 FPGA 之旅的起點,點亮一盞明燈,讓你更有方向感地踏上這段精彩的旅程!

常見相關問題與專業詳細解答

Q1: FPGA 設計一定需要用 Verilog 或 VHDL 嗎?有沒有其他方法?

A1: 嚴格來說,目前市面上絕大多數商業 FPGA 的設計,都離不開 Verilog 或 VHDL。這兩種語言是業界標準,被 EDA 工具鏈完全支援,並且有著成熟的生態系統。當然,也有一些高階的抽象方法,例如使用高階合成 (High-Level Synthesis, HLS) 工具,可以直接將 C/C++ 程式碼轉換成 HDL。這對於熟悉軟體開發的工程師來說,可以大大加速開發流程,特別是在演算法實現和軟硬體協同設計方面。然而,HLS 工具產生的 HDL 程式碼,其效率和可控性有時不如手寫的 HDL,而且對於底層的硬體優化,手寫 HDL 仍然有其不可替代的優勢。所以,對於核心邏輯或性能要求極高的部分,手寫 HDL 依然是主流。

Q2: Verilog 和 VHDL 哪個更容易學?

A2: 這是一個很主觀的問題,很大程度上取決於你的背景。如果你有 C 語言、C++ 或 Java 的編程經驗,你會發現 Verilog 的語法更加親切,因為它借鑒了 C 語言的風格。學習曲線可能會相對平緩一些。而 VHDL 的語法更為嚴謹,結構化程度更高,類似於 Ada 語言。它的類型檢查非常嚴格,這對於防止在設計早期出現一些微妙的錯誤非常有幫助。對於沒有太多編程背景,或者偏好更結構化、模組化設計風格的人來說,VHDL 也可能是一個不錯的選擇。我的建議是,可以先都簡單了解一下,然後選擇一個開始深入學習。重要的是要掌握 HDL 的核心概念,而不是糾結於哪種語法「絕對」更好。

Q3: FPGA 的硬體描述語言跟一般的軟體程式語言有什麼根本區別?

A3: 這點我前面有稍微提到,但我們可以更深入地來說。最根本的區別在於「描述對象」。一般的軟體程式語言(如 C、Python)是用來描述「演算法」的,也就是告訴電腦「如何一步步執行」來完成某個任務。它們通常是順序執行的,並且運行在一個已經固定好的硬體架構(CPU)上。而 FPGA 的硬體描述語言 (HDL) 則是用來描述「硬體結構」和「硬體行為」的。我們不是在寫執行指令,而是在「設計硬體電路」。HDL 的描述最終會被轉換成 FPGA 內部可配置邏輯單元(如 LUT、觸發器)和它們之間的連線。這意味著,HDL 的描述是「並行」的,因為硬體電路本身就是並行工作的。 HDL 的重點在於描述「電路長什麼樣子」,以及「電路如何響應時脈和輸入信號」,而不是「如何一步步去計算」。

Q4: 什麼是「可綜合 (Synthesizable)」的 HDL 程式碼?我該如何確保我的程式碼是可綜合的?

A4: 「可綜合」的 HDL 程式碼,是指那些能夠被綜合工具成功轉換成 FPGA 硬體電路描述的程式碼。有些 HDL 的語句或結構,雖然在模擬器中可以執行,但無法對應到 FPGA 的具體硬體元件。例如,某些進階的變數操作、模擬專用的語句、或者不確定的迴圈次數,都可能導致程式碼無法被綜合。要確保程式碼是可綜合的,通常需要遵循以下原則:

- 使用組合邏輯和時序邏輯的標準結構:例如,組合邏輯使用 `assign` 語句或 `always @(*)` 塊,時序邏輯使用 `always @(posedge clk)` 塊。

- 謹慎使用迴圈和條件語句:對於有限次數且確定的迴圈(如 `for` 迴圈),可以被綜合。但不確定的迴圈(如 `while` 迴圈,直到某個條件滿足才停止)通常無法綜合。條件語句(`if-else`、`case`)的使用方式也需要注意,要確保它們能映射到 Multiplexer 或邏輯閘。

- 注意變數類型和賦值方式:理解阻塞性賦值 (`=`) 和非阻塞性賦值 (`<=`) 在時序邏輯中的應用。

- 參考各 FPGA 廠商的綜合指南:不同的綜合工具對 HDL 的支援程度略有差異,閱讀相應的工具手冊和綜合指南,了解哪些結構是支援的,哪些是不支援的,是非常重要的。

- 多做模擬和綜合測試:在開發過程中,經常進行模擬和綜合,並仔細查看綜合報告,檢查是否有綜合警告或錯誤。

Q5: FPGA 開發中的「時序約束」到底有多重要?如果我不設時序約束會怎麼樣?

A5: 時序約束(Timing Constraints)在 FPGA 開發中,其重要性怎麼強調都不為過。它就像是你給設計下達的「性能指標」和「工作條件」。你可以把它想像成,你要蓋一座橋,時序約束就是告訴你這座橋需要承受多大的載重、能讓多少車輛在一定時間內通過、以及它必須在什麼樣的風速下都能穩定。如果你不設定時序約束,綜合和實現工具就不知道你的設計目標是什麼。它可能會生成一個功能正確,但運行速度非常慢的電路,或者它會盡量優化,但可能不是你真正想要的。在這種情況下,你下載到 FPGA 的比特流,很可能無法達到你期望的工作頻率,甚至根本無法穩定運行。因此,準確設定時脈頻率、輸入輸出延遲、和時脈之間的關係等時序約束,是確保 FPGA 設計能夠達到預期性能的關鍵步驟。