CMRR是什麼?深度解析共模抑制比的奧秘與應用

你是不是也曾遇過類似的困擾呢?小陳是一位熱愛電子設計的工程師,最近他在開發一套高精度感測器系統時,總是遇到一個揮之不去的夢魘:訊號裡夾雜著惱人的雜訊,讓量測數據忽高忽低,完全無法達到設計目標。他嘗試了各種屏蔽、濾波手段,但效果始終不彰。直到有一天,一位經驗豐富的前輩點醒他:「小陳啊,你有沒有仔細看過你選用放大器的 CMRR 指標?」小陳這才恍然大悟,原來這就是問題的癥結所在。

那麼,CMRR是什麼?簡單來說,CMRR (Common-Mode Rejection Ratio),中文稱為「共模抑制比」,它是一個衡量電子電路(特別是差動放大器或運算放大器)抑制「共模訊號」能力的關鍵性能指標。它代表了電路區分有用「差模訊號」與無用「共模雜訊」的效率。這項數值越高,表示電路在面對環境雜訊時,能更有效地將其排除,只專注於處理我們真正感興趣的訊號。對於追求精準度與穩定性的電子設計而言,了解並優化CMRR絕對是不可或缺的一環。

Table of Contents

為什麼CMRR如此重要?從雜訊說起

在現實世界中,任何電子訊號傳輸都難以避免各種「雜訊」的侵擾。這些雜訊可能來自四面八方:電源供應器的漣波、電磁干擾 (EMI)、射頻干擾 (RFI)、地迴路 (Ground Loop) 引起的電壓差異,甚至是鄰近線路之間的串擾。這些雜訊往往會以兩種形式影響我們的訊號:

- 差模雜訊 (Differential-Mode Noise):直接疊加在我們感興趣的差模訊號上,與有用訊號的性質相似,較難區分。

- 共模雜訊 (Common-Mode Noise):同時、同相地出現在兩條輸入線上。它通常是環境干擾的結果,對我們真正的訊號而言,幾乎是完全無用的「搭便車」成分。

想像一下,你想要測量一個微弱的電壓差(這是我們的有用差模訊號),但同時,你的感測器訊號線卻像天線一樣,捕捉到了周圍環境的電磁波干擾,這些干擾在兩條訊號線上幾乎是同步出現的,這就是典型的共模雜訊。如果電路無法有效抑制這些共模雜訊,它們就會被放大器一併放大,最終淹沒掉我們真正想要的微弱訊號,導致量測結果失真、不穩定。

這就像是你在一個吵雜的演唱會現場,試圖跟朋友講悄悄話。差模訊號就是你的悄悄話,而共模雜訊就是整個會場的喧囂。如果你的耳朵(放大器)無法辨識並忽略這些喧囂,你就根本聽不清楚朋友說了什麼。因此,一個高的CMRR就顯得至關重要,它讓我們的電路能夠在喧囂的環境中,「聰明地」只聽取真正重要的聲音。

深入剖析CMRR:理論基礎與計算方式

要真正理解CMRR,我們必須先弄清楚共模訊號與差模訊號的定義,以及它們如何影響放大器的運作。

什麼是共模訊號與差模訊號?

對於一個具有兩個輸入端(V+ 和 V-)的差動放大器來說:

- 差模訊號 (Vd):指兩個輸入端之間的電壓差。這通常是我們想要測量的有用訊號。

Vd = V+ - V- - 共模訊號 (Vc):指兩個輸入端相對於地參考點的平均電壓。它代表了兩個輸入端共同存在的成分,通常是雜訊或偏移量。

Vc = (V+ + V-) / 2

舉個例子,如果你的感測器輸出 V+ = 1.001V 和 V- = 1.000V。那麼:

- 差模訊號 Vd = 1.001V – 1.000V = 0.001V (1mV)。這是我們真正想測量的微小訊號。

- 共模訊號 Vc = (1.001V + 1.000V) / 2 = 1.0005V。這個值可能來自於感測器輸出的直流偏置或環境雜訊。

一個理想的差動放大器應該只放大 Vd,而完全忽略 Vc。但現實中,沒有放大器是完美的。

共模抑制比 (CMRR) 的數學表達

CMRR正是用來量化這種「理想與現實」之間差異的指標。它的定義是差模增益 (Ad) 與共模增益 (Ac) 的比值。

CMRR = Ad / Ac

- Ad (Differential Gain):差動放大器對差模訊號的放大倍數。它代表了放大器將有用訊號放大的能力。

- Ac (Common-Mode Gain):差動放大器對共模訊號的放大倍數。這是一個不希望出現的增益,理想情況下應該是零。

由於CMRR的數值範圍可能非常大,為了方便表達和比較,通常會用分貝 (dB) 來表示:

CMRR (dB) = 20 * log10 (Ad / Ac)

舉例來說:

- 如果一個放大器的 Ad = 100,而 Ac = 0.01,那麼 CMRR = 100 / 0.01 = 10000。

換算成 dB,CMRR (dB) = 20 * log10 (10000) = 20 * 4 = 80 dB。 - 這意味著,對於相同大小的輸入訊號,差模訊號被放大了100倍,而共模訊號只被放大了0.01倍。兩者之間存在著10000倍的抑制能力。

我的觀點是:當我們看到放大器規格書上的CMRR值時,應該立即將其視為這款晶片在「抗干擾」能力上的成績單。數值越高,成績越好,代表它在嘈雜環境下能更清晰地處理我們的訊號。這不只是一個數字,更是系統穩定性和精準度的強力保證。

理想情況與現實挑戰

在理想的差動放大器模型中,共模增益 Ac 應該為零,因此 CMRR 會趨近於無限大。這表示它能夠完美地忽略所有共模訊號。

然而,現實世界中的放大器,無論是獨立的差動放大器還是運算放大器,都無法達到這樣的完美。由於晶片內部元件(電阻、電晶體等)的製造公差、溫度變化、寄生效應等因素,導致輸入級的匹配總是不完美的。這種不匹配會讓共模訊號在一定程度上被「誤判」為差模訊號,進而被放大,產生一個非零的共模增益 Ac。因此,所有真實的電子電路都會有一個有限的 CMRR 值。

影響CMRR的關鍵因素

理解影響CMRR的因素,對於設計者來說至關重要。這能幫助我們在選材和佈局時做出明智的選擇。

1. 元件匹配度

這絕對是影響CMRR最核心的因素。在差動放大器的輸入級,通常會有對稱的電阻、電晶體或場效應電晶體。如果這些對稱元件的參數(例如電阻值、電晶體增益等)不完全匹配,那麼即使是純粹的共模訊號,也會在兩條輸入路徑上產生微小的電壓差異,進而被放大器「誤認為」是差模訊號。

我的經驗是:在高精度的應用中,即使是0.1%的電阻不匹配,都可能顯著降低整個電路的CMRR,讓原本微弱的雜訊變得清晰可見。

2. 頻率響應

你會發現,幾乎所有放大器的規格書都會指出,其CMRR性能會隨著頻率的升高而顯著下降。這是因為在高頻下:

- 寄生電容效應:電路板上的走線、元件封裝內部都會存在微小的寄生電容。這些電容在高頻下會形成不同的阻抗路徑,破壞輸入級的對稱性,導致共模訊號的抑制能力下降。

- 增益頻寬積 (Gain-Bandwidth Product, GBP):放大器的增益會隨著頻率升高而下降。而共模抑制能力也受到內部電路增益的影響,當高頻下增益下降時,抑制雜訊的能力也會隨之減弱。

這就好像,在安靜的環境下,你能輕易地分辨出兩段不同的聲音;但在嘈雜又快速變化的環境中,你的分辨能力就會下降。所以,對於處理高頻訊號的電路,選擇在目標頻率範圍內仍能維持高CMRR的放大器尤為重要。

3. 電源供應

放大器的電源供應必須保持穩定、低雜訊。如果電源電壓存在漣波或瞬時波動,這些雜訊可能會透過放大器內部電路耦合到訊號路徑中。雖然電源雜訊主要由 PSRR (Power Supply Rejection Ratio) 來衡量,但劣質的電源也會間接惡化CMRR,因為電源不穩定可能導致內部偏置點漂移,影響元件匹配度。

4. 佈線與接地

電路板的佈局和接地設計對CMRR有著不可忽視的影響。糟糕的佈線可能導致:

- 不對稱走線:輸入訊號線長度不一致、走線靠近不同雜訊源,會導致兩條輸入線上感應到的雜訊不一致,使共模雜訊轉化為差模雜訊。

- 地迴路:當接地路徑形成一個迴路時,外部磁場可能在其中感應出電流,產生地面電壓差,進而影響訊號的共模成分。

我的評論:很多時候,我們耗費巨資選用高性能晶片,卻敗在不佳的佈局上。這真是「一失足成千古恨」的典型案例!

CMRR在實際應用中的重要性

CMRR不只是一個理論概念,它在許多實際應用中扮演著舉足輕重的角色,直接影響系統的效能和可靠性。

儀器放大器 (Instrumentation Amplifier)

儀器放大器是CMRR應用最典型的代表。它們專為高精度、小訊號的差動放大而設計,廣泛應用於感測器介面(如應變規、熱電偶、壓力感測器等)。這些感測器通常會輸出非常微弱的差動訊號,且常常處於充滿電磁雜訊的工業環境中,或者訊號線路很長,容易感應雜訊。

儀器放大器之所以能脫穎而出,就是因為其內部設計(通常由三個運算放大器構成)能夠提供極高的CMRR(很多高端儀器放大器可達100dB甚至更高),有效抑制長導線或惡劣環境中引入的共模雜訊,確保微弱的感測器訊號被精準放大,而不受干擾影響。可以說,沒有高CMRR,儀器放大器就失去了其核心價值。

運算放大器 (Operational Amplifier, Op-Amp)

雖然運算放大器本身不是專門的差動放大器,但當它被配置成差動放大電路時,其CMRR性能同樣重要。在非反相和反相輸入端訊號來源不匹配的情況下,運算放大器的CMRR決定了它能多好地拒絕共模雜訊。這對於精密的訊號調節、濾波和電壓比較等應用至關重要。

資料擷取系統 (Data Acquisition Systems, DAQ)

資料擷取系統的任務是將真實世界的類比訊號轉換為數位數據供電腦處理。在工業控制、科學研究等領域,DAQ系統往往需要從各種感測器中採集多個通道的訊號。如果每個通道的放大器CMRR不高,那麼輸入的共模雜訊就會轉換為差模訊號,被數位化後污染數據,導致量測結果的不準確,甚至影響後續的決策和控制。因此,高CMRR是DAQ系統確保數據完整性和精準度的基石。

醫療電子設備

在醫療領域,許多設備需要擷取人體內非常微弱的生理訊號,例如心電圖 (ECG)、腦電圖 (EEG) 或肌電圖 (EMG)。這些訊號的電壓通常只有微伏到毫伏等級,而且人體本身就是一個巨大的雜訊接收天線,容易從電源線、周圍電器感應到強烈的50/60 Hz市電雜訊。

高CMRR的放大器在這裡就發揮了關鍵作用,它能夠有效地抑制這些來自環境的共模市電雜訊,突出微弱的生理差模訊號,確保醫生能夠獲得清晰、準確的診斷數據。這是人命關天的大事,CMRR的表現直接影響診斷的準確性和治療的有效性。

如何提升電路的CMRR?實用設計指南

了解了CMRR的重要性後,接下來我們來談談在實際設計中,有哪些方法可以幫助我們提升電路的共模抑制能力。這是我多年來的一些實用建議,希望能給你一些啟發。

1. 選擇高品質元件

這是最直接也最基礎的步驟。從源頭抓起,選用本身就具有高CMRR性能的積體電路 (IC)。

- 專用儀器放大器:對於需要極高CMRR的應用,直接選擇專為此目的設計的儀器放大器 (Instrumentation Amplifier),它們的內部架構就已經針對共模抑制進行了優化。

- 精密運算放大器:如果使用運算放大器搭建差動電路,務必查閱規格書,選擇CMRR標稱值較高的精密運算放大器。

- 低公差電阻:搭配使用匹配度高、溫度係數低的精密電阻。例如,0.1%甚至0.01%公差的電阻,可以最大限度地減少因電阻不匹配引起的共模增益。

2. 精確匹配電阻

即使選用了低公差電阻,它們之間仍然可能存在微小的差異。在關鍵的差動放大電路中,輸入級和回饋網路的電阻匹配度至關重要。

- 使用電阻陣列:選用整合在單一封裝中的電阻陣列 (Resistor Array),它們通常在同一晶片上製造,因此具有極佳的匹配度和熱追蹤特性,優於分立的單個電阻。

- 雷射修整 (Laser Trimming):對於一些高階儀器放大器,製造商會採用雷射修整技術,在晶片製造過程中精確調整電阻值,以達到近乎完美的匹配度,從而獲得極高的CMRR。

- 手動匹配 (限於原型階段):在一些原型開發或小批量生產中,甚至可以透過人工測量和挑選,將最匹配的電阻配對使用。

3. 優化電路佈局

電路板佈局對於高頻CMRR尤其關鍵。好的佈局能有效減少雜訊耦合,保持訊號對稱性。

- 對稱佈局:讓差動輸入訊號的兩條走線(例如V+和V-)盡可能地長度相等、寬度一致,並且平行靠近佈置。這樣可以確保它們感應到相似的電磁干擾,維持共模特性。

- 縮短走線:將差動輸入訊號線盡可能地縮短,減少其作為天線接收雜訊的機會。

- 避免耦合:讓差動輸入線遠離其他高頻或高電流的訊號線,避免串擾。如果必須交叉,應盡量垂直交叉。

- 良好接地設計:採用星狀接地 (Star Grounding) 或多點接地策略,確保訊號地和電源地有清晰、低阻抗的路徑回到共同參考點。避免形成地迴路。地平面 (Ground Plane) 的使用也能有效降低接地阻抗,減少共模雜訊。

- 隔離保護:對於非常敏感的輸入訊號,可以考慮使用保護環 (Guard Ring) 或屏蔽線,將輸入訊號與周圍雜訊隔離開來。

4. 濾波技術

適當的濾波可以在不同階段幫助改善CMRR。

- 輸入端共模濾波器:在差動放大器輸入端加裝共模扼流圈 (Common-Mode Choke) 和/或共模電容,可以直接濾除進入電路的共模雜訊。這是一種非常有效的方法。

- 差模濾波器:雖然不是直接提升CMRR,但在輸入端加入差模濾波器(例如RC濾波器),可以濾除高頻差模雜訊,同時也要注意不要破壞共模的平衡。

5. 電源去耦與穩壓

清潔穩定的電源是電路正常運行的基礎,也能間接改善CMRR。

- 去耦電容:在放大器IC的電源引腳附近放置多個不同容量的去耦電容(例如一個0.1μF陶瓷電容和一個10μF電解電容),以濾除高頻和低頻電源雜訊。

- 穩壓器:使用低雜訊、高PSRR的穩壓器為放大器提供電源。

6. 考慮頻率效應

由於CMRR隨頻率下降,在設計時必須仔細評估目標頻率範圍內的CMRR性能。如果需要在高頻下保持高CMRR,可能需要選用頻寬更高、設計更精良的放大器,或者在輸入端採用共模濾波來處理。

案例探討:CMOS製程對CMRR的影響

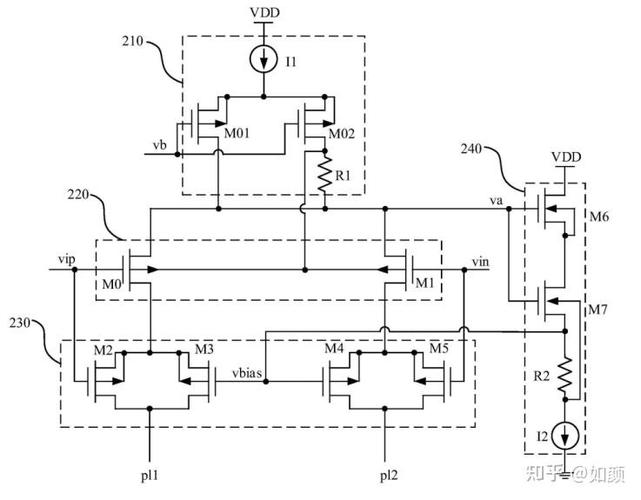

在現代的積體電路設計中,CMOS(互補金屬氧化物半導體)製程是主流。CMOS放大器的CMRR表現,很大程度上取決於其輸入差動對的匹配程度。然而,CMOS製程本身在元件匹配上存在一些固有的挑戰。

一個典型的CMOS差動對,是由兩個匹配的NMOS或PMOS電晶體組成。儘管設計者會盡力讓它們的尺寸、佈局完全一致,但在實際的晶圓製造過程中,仍然會存在微觀層面的不均勻性。例如,氧化層厚度、通道摻雜濃度、閾值電壓等都可能存在微小差異。這些差異會導致兩個電晶體的跨導 (transconductance, Gm) 和輸出電阻 (ro) 產生不匹配,進而使得共模訊號無法被完美抑制。

為了克服這些挑戰,現代CMOS放大器設計會採用多種技術來提升CMRR:

- 版圖設計技巧:採用交錯式佈局 (interdigitated layout) 或共中心佈局 (common-centroid layout),使匹配的電晶體在物理上盡可能地靠近,並通過將單個大電晶體分解為多個小單元並均勻分佈,以平均化製程不均勻性帶來的影響。

- 電流鏡匹配:精確設計用於偏置差動對的電流鏡,確保電流匹配度高,從而穩定差動對的工作點。

- 增益級設計:在差動對之後增加高增益的級聯放大器,可以放大差模訊號,同時利用整體電路的回饋來減少共模訊號的相對影響。

我的觀察是:CMOS製程的微型化趨勢,雖然帶來了更高的集成度和更低的功耗,但也加劇了元件不匹配帶來的挑戰。因此,優秀的類比IC設計師在設計CMOS放大器時,對版圖和電路拓撲的精細掌控,是實現高CMRR的關鍵所在。

CMRR的量測方法簡述

想要知道一個放大器的CMRR到底有多少,最直接的方法當然是實際量測。雖然這通常是專業實驗室的工作,但理解其原理對我們也很有幫助。

量測CMRR的基本步驟如下:

- 量測差模增益 (Ad):

- 將一個小的差模輸入訊號 (Vd_in) 施加到放大器輸入端(例如,讓 V+ 和 V- 之間存在一個電壓差)。

- 量測輸出訊號 (Vo_d)。

- 計算 Ad = Vo_d / Vd_in。

- 量測共模增益 (Ac):

- 將一個共模輸入訊號 (Vc_in) 施加到放大器輸入端(例如,將 V+ 和 V- 短接在一起,然後施加一個共同的電壓)。

- 量測輸出訊號 (Vo_c)。

- 計算 Ac = Vo_c / Vc_in。

- 計算 CMRR:

- 使用公式 CMRR = Ad / Ac。

- 若要轉換為分貝,則為 CMRR (dB) = 20 * log10 (Ad / Ac)。

在實際操作中,為了獲得準確的結果,量測時需要注意訊號產生器的精度、示波器的量測解析度、以及避免額外的雜訊引入。此外,通常會在不同頻率下進行量測,以獲得完整的CMRR頻率響應曲線。

常見問題 (FAQ)

在理解CMRR的過程中,許多人會有一些常見的疑問。我在這裡整理了一些問題,並提供我的專業解答。

Q1:CMRR越高越好嗎?

答案是:通常情況下,是的,CMRR越高越好。更高的CMRR意味著放大器能夠更有效地抑制共模雜訊,從而提供更清晰、更準確的訊號放大。在諸如醫療設備、高精度感測器接口或工業控制等應用中,對CMRR的要求往往非常高,因為微弱的有用訊號很容易被環境雜訊所淹沒。

然而,我們也需要考慮實際的工程權衡。追求極致的CMRR往往會帶來更高的成本、更複雜的電路設計,甚至可能影響到其他性能指標,例如頻寬或功耗。對於一些對雜訊容忍度較高的應用,或是在成本預算非常緊張的情況下,一味地追求最高CMRR可能並非最優解。設計者需要根據具體的應用場景、預期的雜訊水平和所需的訊號精準度,來選擇一個「足夠好」的CMRR水平。

Q2:CMRR和PSRR(電源抑制比)有什麼關係?

答案是:CMRR和PSRR都是衡量放大器抑制雜訊能力的指標,但它們針對的雜訊來源不同。

- CMRR (Common-Mode Rejection Ratio):衡量放大器抑制「輸入端」共模雜訊的能力。這種雜訊是通過輸入訊號線進入放大器的。

- PSRR (Power Supply Rejection Ratio):衡量放大器抑制「電源供應器」雜訊(如電源漣波、電源線上的突波)的能力。這種雜訊是通過電源引腳進入放大器的。

雖然它們針對的雜訊來源不同,但兩者之間有著間接的關聯。一個低PSRR的放大器,其電源上的雜訊可能會耦合到其內部電路中,影響其偏置點的穩定性,進而可能間接降低其對共模訊號的抑制能力,也就是會影響CMRR。因此,在設計一個低雜訊系統時,通常需要同時關注放大器的CMRR和PSRR性能,確保從輸入端和電源端引入的雜訊都能得到有效抑制。它們是共同保障訊號完整性的「好夥伴」。

Q3:為什麼高頻下的CMRR會下降?

答案是:高頻下CMRR下降是一個非常普遍的現象,主要原因有兩個:

- 寄生電容效應:隨著頻率升高,電路板走線、元件封裝內部以及晶片內部電晶體之間的微小寄生電容開始發揮作用。這些寄生電容會形成不同的交流阻抗路徑,打破原本在低頻下非常平衡的差動輸入級。一旦平衡被破壞,即使是純粹的共模訊號,也會在兩條輸入路徑上產生不同的衰減或相移,導致一部分共模訊號轉化為差模訊號,進而被放大器放大,從而降低了共模抑制能力。

- 放大器增益頻寬特性:放大器本身的增益會隨著頻率升高而下降。當頻率高到一定程度時,放大器內部抑制共模訊號的增益級可能已經不足以有效工作。這就像一艘船,在平靜水域航行時能很好地保持平衡,但在風高浪急的大海上,就難以維持同樣的穩定性了。

因此,在設計高頻應用時,我們不僅要選擇具有高CMRR的放大器,更要仔細查閱其規格書中提供的「CMRR vs. Frequency」曲線圖,確保在目標工作頻率範圍內,其CMRR仍然能夠滿足系統的需求。這通常也是許多工程師容易忽略但又非常關鍵的一個細節。

Q4:在設計時,應該如何平衡成本與CMRR性能?

答案是:平衡成本與性能是電子設計中永恆的課題,對於CMRR也不例外。我的建議是:

- 評估應用需求:首先,清楚地定義你的應用對雜訊容忍度和精準度的要求。是需要極致的奈伏級精度,還是毫伏級就足夠?是在惡劣的工業環境,還是在相對乾淨的實驗室?這些都會直接影響所需的CMRR水平。

- 分析雜訊來源:了解你設計所處的環境中可能存在的共模雜訊水平。例如,如果距離市電雜訊源很近,或者訊號線路很長,那麼就需要更高的CMRR。

- 從整體系統考慮:不要只看單個放大器的CMRR。有時候,透過更好的屏蔽、接地設計、輸入濾波等系統級手段,即使使用CMRR稍低的放大器,也能達到令人滿意的效果。這可能比直接選用最昂貴的高CMRR放大器更具成本效益。

- 分階段優化:在原型設計階段,可以先選擇一個性能足夠的晶片進行驗證。如果發現雜訊問題,再逐步升級元件,例如從普通電阻升級到精密電阻,或者從標準運算放大器升級到儀器放大器。這樣可以避免一開始就過度設計和浪費資源。

- 查閱替代方案:市面上有許多不同價格和性能等級的放大器可供選擇。花時間比較不同廠家的產品規格書,通常能找到在預算範圍內性能最佳的解決方案。

總之,沒有「一刀切」的答案。關鍵在於深入理解你的設計目標、環境限制和可用資源,然後做出明智的權衡。

Q5:如何快速判斷一個放大器的CMRR是否足夠應用?

答案是:要快速判斷,可以從以下幾個方面入手:

- 查閱數據手冊:這是最直接且權威的方式。所有正規的放大器都會在數據手冊(datasheet)中明確標註CMRR值,通常會提供在不同頻率下的曲線圖。你需要關注在你的應用工作頻率下的CMRR值。

- 估算所需的抑制倍數:

- 確定你的有用差模訊號的最小幅值 (Vd_min)。

- 估計你環境中可能存在的共模雜訊的最大幅值 (Vc_max)。

- 設定你希望雜訊對有用訊號的影響比例(例如,希望雜訊比有用訊號低1000倍,即 -60dB)。

- 那麼,你需要的CMRR約等於 `20 * log10 (Vc_max / (Vd_min * noise_ratio))`。舉例,如果 Vd_min = 1mV,Vc_max = 1V (1000mV),希望雜訊比訊號低10倍,那麼 Ac * Vc_max < Vd_min / 10。因此 Ac < (Vd_min/10) / Vc_max = (0.1mV)/1000mV = 0.0001。而 Ad 假設為 100,則 CMRR = Ad/Ac = 100/0.0001 = 1,000,000,即 120dB。

- 參考類似應用:如果你的應用與某些常見應用類似(如ECG、應變規等),可以參考行業標準或已有的成功設計所使用的放大器CMRR等級。這能提供一個很好的起點。例如,醫療ECG前端通常要求至少80dB甚至100dB以上的CMRR。

- 考慮輸入級拓撲:一般來說,專用的儀器放大器由於其內部的三運放或兩運放架構,天生就比單個運算放大器配置的差動放大電路具有更高的CMRR。這是因為儀器放大器在輸入端實現了高輸入阻抗和良好的共模抑制。

總之,透過綜合考量數據手冊指標、你的具體需求和應用場景,你就能比較快速地判斷所選放大器的CMRR是否足夠,確保設計的穩定與可靠。