什麼是扇形晶圓級封裝:深度解析其技術、優勢與應用

Table of Contents

什麼是扇形晶圓級封裝?核心概念解析

在當今瞬息萬變的半導體產業中,晶片尺寸不斷縮小,功能卻日益強大。這背後除了晶圓製造技術的進步外,先進的封裝技術也扮演著舉足輕重的作用。其中,扇形晶圓級封裝(Fan-Out Wafer-Level Packaging, FoWLP)作為一項突破性的創新,正逐漸成為高性能、小型化電子產品的核心。

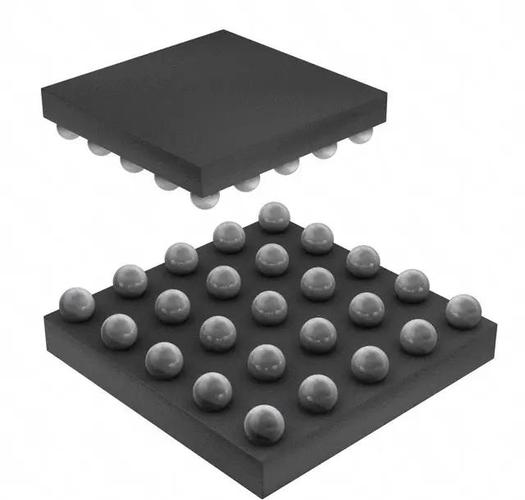

那麼,究竟什麼是扇形晶圓級封裝呢?簡單來說,它是一種將多個積體電路(IC)晶片在一個「重構晶圓(Reconstituted Wafer)」上進行整合,並將其連接點(I/O)從晶片本身的邊界向外「扇形」延伸的先進封裝技術。這與傳統的「扇入(Fan-In)」晶圓級封裝不同,後者的I/O點位於晶片內部或其正下方,限制了I/O的數量與佈局彈性。

FoWLP的出現,旨在解決傳統封裝技術在晶片尺寸縮小、I/O數量增加、電氣性能提升以及成本控制方面所面臨的挑戰。它透過創新的工藝流程,實現了更小的封裝尺寸、更優異的電氣與散熱性能,同時為異質整合(Heterogeneous Integration)提供了廣闊的平台。

扇形晶圓級封裝的運作原理

要深入理解FoWLP,我們必須剖析其獨特的製程步驟。與傳統先切割再封裝的方式不同,FoWLP是在「晶圓級」別進行大部分的封裝工作,這顯著提高了生產效率和成本效益。

1. 晶片黏合與模塑成型 (Die Mounting & Molding)

- 晶片揀選與放置: 首先,從完成晶圓測試(Wafer Sort)的原始晶圓上,挑選出已知合格(Known Good Dies, KGD)的裸晶(bare dies)。這些裸晶會被精確地放置在一個預先準備好的載板(Carrier Wafer)上,晶片之間留有適當的間距,這個間距將用於後續的扇出佈線。

- 模塑成型: 接著,在載板上的晶片周圍和上方,注入特殊的環氧模塑化合物(Epoxy Molding Compound, EMC)。這種化合物會將所有裸晶包裹起來,形成一個新的「重構晶圓」或稱「模塑晶圓(Molded Wafer)」。這個模塑晶圓的尺寸可能與原始晶圓相同,甚至更大,取決於設計需求。

2. 載板移除與重分佈層形成 (Carrier Removal & Redistribution Layer Formation)

- 載板移除: 模塑固化後,原始的載板會被移除。此時,裸晶的正面(Active Side)朝上,被穩固地嵌入在模塑化合物中。

- 表面處理: 對模塑晶圓的表面進行平坦化(Planarization)處理,確保表面光滑平整,為後續的佈線層做好準備。

- 重分佈層 (Redistribution Layer, RDL) 形成: 這是FoWLP的核心步驟之一。利用標準的薄膜製程(如光刻、濺鍍、電鍍等),在模塑晶圓表面製作多層金屬互連線路。這些線路將晶片原本的I/O焊墊向外延伸,甚至超出晶片的物理邊界,形成扇形佈局,這就是「扇形」一詞的由來。RDL層不僅用於延伸I/O,也可以包含被動元件(如電容、電阻)或用於電源/接地分配。

3. 凸塊形成與切割 (Bumping & Dicing)

- 凸塊形成: 在RDL層的終端接點上,透過電鍍或印刷等方式,形成微型金屬凸塊(Solder Bumps或Copper Pillars)。這些凸塊是封裝後的IC與外部電路板連接的介面。

- 切割與測試: 最後,將完成所有封裝工藝的重構晶圓切割成單個的封裝單元。每個單元都經過最終測試,以確保其功能和性能符合要求,成為可供使用的FoWLP元件。

FoWLP的創新之處在於它打破了傳統封裝中I/O受晶片尺寸限制的格局,透過模塑重構和RDL技術,實現了更高的I/O密度和更靈活的佈線,為晶片設計帶來了前所未有的自由度。

扇形晶圓級封裝的關鍵優勢

FoWLP之所以被視為半導體封裝領域的「明日之星」,主要歸因於其一系列顯著的優勢:

- 小型化與輕量化:

由於取消了傳統封裝所需的基板和引線框架,FoWLP封裝後的尺寸顯著縮小,厚度也大幅降低。這使得電子產品可以設計得更加輕薄,符合行動裝置等應用對體積的嚴苛要求。

- 優異的電氣性能:

RDL層的金屬線路較短且寬,減少了電阻、電感和電容效應。這意味著信號傳輸損耗更低,能夠支持更高的時脈速度,提供更優越的電氣性能,對於高效能運算(HPC)和射頻(RF)應用至關重要。

- 卓越的散熱管理:

晶片直接嵌入模塑化合物中,且RDL層提供了一定的散熱路徑,使得FoWLP在散熱方面表現優異。這有助於降低晶片工作溫度,提升元件的可靠性和壽命。

- 更高的I/O密度:

扇形佈局使得I/O點可以延伸到晶片實際邊界之外,大大增加了單位面積內的I/O數量。這對於具備大量輸入/輸出需求的複雜系統級晶片(SoC)尤其重要。

- 成本效益(長期而言):

雖然初期設備投資較高,但FoWLP在晶圓級別進行大規模生產,通過攤薄單位晶片的製造成本,長期來看具有更高的成本效益,特別是對於大量生產的消費性電子產品。

- 多晶片整合潛力:

FoWLP平台可以容納多個不同功能的裸晶(如邏輯晶片、記憶體、射頻模組等),實現異質整合。這使得單一封裝內可以集成更複雜的系統功能,簡化了電路板設計,並提升了整體系統性能。

扇形晶圓級封裝的廣泛應用

憑藉其獨特的優勢,FoWLP已在多個高科技領域找到了廣闊的應用空間:

- 行動與消費性電子:

智慧型手機、平板電腦、穿戴式裝置等對體積、功耗和性能有極高要求的產品,是FoWLP最早也是最主要的應用市場。例如,蘋果公司在其A系列應用程式處理器(APU)中便大量採用了FoWLP技術,以實現極致的輕薄與強大性能。

- 汽車電子:

隨著自動駕駛和車載資通訊系統的發展,汽車電子需要更高的可靠性、更強大的運算能力和更好的散熱管理。FoWLP的堅固性、小型化和優異性能使其成為ADAS(先進駕駛輔助系統)、車載娛樂系統和電源管理模組的理想選擇。

- 人工智慧與高效能運算 (AI & HPC):

AI晶片和伺服器CPU/GPU對高頻寬記憶體(HBM)和多晶片整合的需求日益增長。FoWLP能夠提供高密度的互連和優異的電氣性能,使其成為集成這些複雜系統的關鍵技術。

- 物聯網 (IoT):

IoT設備通常體積小巧,對低功耗和高度集成有要求。FoWLP能夠將多個傳感器、處理器和無線通訊模組整合在一個微型封裝中,滿足IoT設備的特定需求。

- 5G通訊:

5G技術對射頻(RF)模組的性能、尺寸和散熱提出了新的挑戰。FoWLP能夠有效地集成RF前端模組,提供更佳的訊號完整性和更小的佔板空間。

扇形晶圓級封裝面臨的挑戰

儘管FoWLP技術前景光明,但在其普及和進一步發展的道路上,也存在一些挑戰:

- 翹曲問題 (Warpage):

在模塑成型和後續熱處理過程中,不同材料(裸晶、模塑化合物、RDL金屬層)的熱膨脹係數差異可能導致晶圓或封裝件產生翹曲。這會影響後續製程的精確度,甚至導致良率下降。

- 良率控制 (Yield Control):

FoWLP製程步驟相對複雜,涉及到精密對準和多層薄膜製程。任何一個環節的偏差都可能影響最終的良率,尤其是在處理大尺寸重構晶圓時,如何維持高良率是一個持續的挑戰。

- 設備投資與製程複雜度:

建立FoWLP生產線需要昂貴的精密設備,並且製程開發和優化需要大量的時間和資源。這使得初期投入成本較高,對於規模較小的封測廠而言構成進入門檻。

- 異質整合複雜度:

雖然FoWLP有利於異質整合,但將不同尺寸、不同厚度、不同材料的晶片精確地整合在同一模塑體中,並確保其熱機械穩定性和電氣互連可靠性,仍然是一項複雜的技術挑戰。

扇形晶圓級封裝的未來發展趨勢

面對挑戰,FoWLP技術仍在不斷演進。未來的發展將主要聚焦於:

- 更精細的RDL技術: 實現更細線寬和間距,以支持更高的I/O密度和更複雜的佈線。

- 多層FoWLP結構: 開發3D堆疊的扇形封裝,進一步提升整合度。

- 新材料與新工藝: 探索具有更低熱膨脹係數、更優異電氣性能的模塑材料和更高效的製程工藝,以解決翹曲和提高良率。

- 與其他先進封裝技術的結合: 如與Chiplet(小晶片)技術、高頻寬記憶體(HBM)等結合,打造更高集成度的系統級封裝(SiP)。

結論:扇形晶圓級封裝——引領半導體封裝新紀元

總而言之,扇形晶圓級封裝(FoWLP)不僅是一種先進的半導體封裝技術,更是推動電子產品向更小、更快、更強大方向發展的關鍵力量。它透過創新的「重構晶圓」和「扇形RDL」概念,打破了傳統封裝的物理限制,為晶片設計者提供了前所未有的自由度,並顯著提升了產品的性能和成本效益。

儘管面臨技術和生產上的挑戰,FoWLP在行動通訊、汽車電子、人工智慧和高效能運算等領域的成功應用,已經證明了其巨大的潛力。隨著技術的不斷成熟和工藝的進一步優化,FoWLP無疑將在未來的半導體產業中扮演越來越重要的角色,引領晶片封裝進入一個全新的紀元。

常見問題 (FAQ)

如何區分扇形晶圓級封裝(FoWLP)和傳統封裝?

FoWLP的主要區別在於其「晶圓級」的製程以及I/O點可以「扇形」延伸到晶片實際邊界之外。傳統封裝通常是先切割晶片再進行單個封裝,且I/O受限於晶片尺寸。FoWLP能實現更小的尺寸、更高的集成度和更好的電氣性能。

為何重分佈層(RDL)在扇形晶圓級封裝中如此重要?

RDL是FoWLP的核心技術之一,它允許將晶片上的微小I/O焊墊重新佈線,扇形延伸到晶片邊界之外,形成更大的焊點間距,以便於後續與外部電路板連接。同時,RDL提供高效的電氣互連,減少信號損耗,並能容納多層佈線,支持複雜的電路設計。

扇形晶圓級封裝主要應用於哪些類型的產品?

FoWLP主要應用於對體積、性能和功耗有嚴格要求的產品,例如高階智慧型手機的應用程式處理器(APU)、穿戴式裝置、汽車電子(如ADAS系統)、人工智慧晶片以及5G通訊模組等。其高集成度和優異性能使其成為這些領域的理想選擇。

如何解決扇形晶圓級封裝在製程中可能出現的翹曲問題?

解決FoWLP翹曲問題的方法包括:優化模塑材料的熱膨脹係數,使其與晶片更匹配;調整模塑成型和固化時的溫度曲線;引入應力緩衝層;以及設計更精密的載板和晶片排布,以分散應力。業界也在持續研究新的製程技術和材料來降低翹曲風險。

扇形晶圓級封裝對未來的半導體發展有何影響?

FoWLP對半導體發展的影響深遠,它推動了晶片的小型化和高性能化,為多晶片異質整合提供了理想平台,使得複雜系統級晶片(SiP)的設計成為可能。它降低了單位晶片的封裝成本,加速了高科技產品的普及,並將持續是摩爾定律演進和後摩爾定律時代晶片集成的重要推動力。